CH7523

- 如果您对产品有相关疑问,或者遇到任何,您都可以注册网站帐号,

- 然后到技术支持论坛去提问寻求帮助。

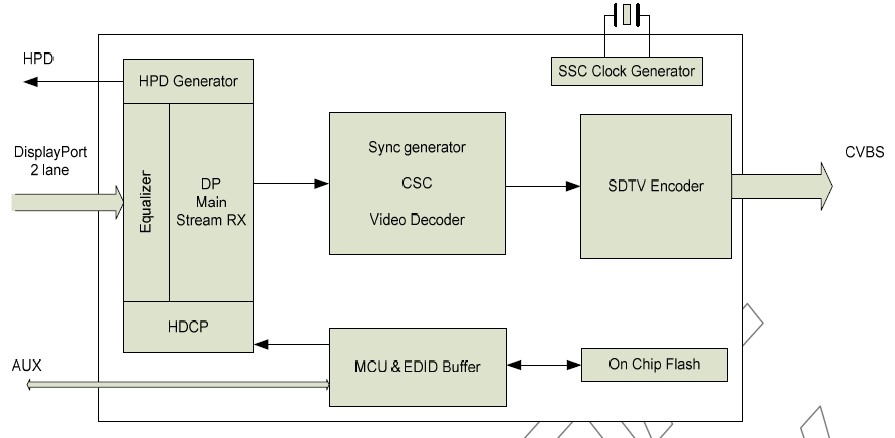

Chrontel’s CH7523 is a low-cost, low-power semiconductor device that translates the DisplayPort signal to the CVBS. This innovative DisplayPort receiver with an integrated SDTV encoder is specially designed to target the DisplayPort Docking Station and Automobile Entertainment Device. Through the CH7523’s advanced decoding / encoding algorithm, the input DisplayPort high-speed serialized multimedia data can be seamlessly converted to SDTV video output.

The CH7523 is compliant with the DisplayPort Specification 1.2. With internal HDCP key Integrated, the device support HDCP 1.3 specifications. In the device’s receiver block, which supports two DisplayPort Main Link Lanes input with data rate running at either 1.62Gb/s or 2.7Gb/s, can accept RGB digital formats in either 18- bit 6:6:6 or 24-bit 8:8:8, and converted the input signal to CVBS/S-Video. Leveraging the DisplayPort’s unique source/sink “Link Training” routine, the CH7523 is capable of instantly bring up the video display to the analog TV when the initialization process is completed between CH7523 and the graphic chip.

With sophisticated MCU and the Boot ROM embedded, CH7523 support auto-boot and EDID buffer. After the configuration by firmware, which is auto loaded from Boot ROM, CH7523 can support DP input detection, TV connection detection and determine to enter into Power saving mode automatically.

Input Interface eDP/DP

Output Interface CVBS

Audio Interface IIS, SPDIF Output

Other features No

Package Type QFN40

Part Number Package Type Operating Temperature Range Minimum Order Quantity

CH7523A-BF 40 QFN, Lead-free Commercial : 0 to 70°C 490/Tray

Oct 2021

昆泰推出支持8K分辨率的DP 1.4 / U...

上...

Jun 2021

昆泰推出兼容DisplayPort和LVDS标...

昆泰推出兼容DisplayPort和LVDS标...

传真:86-21-68791558

总公司网站: www.chrontel.com

电子邮件:ke.liu@chrontel.com.cn

微信公众号:

Copyright © 1998-2023 Chrontel, Inc. All Rights Reserved. 沪ICP备15010045号-1  沪公网安备31011502003526号 隐私保护 法律声明

沪公网安备31011502003526号 隐私保护 法律声明